Supra软件发布更新:AGRV2K CPLD 支持无源晶体作为时钟输入源

Supra最新版本2025.01.b0

1.VE管脚文件设为PIN_HSE

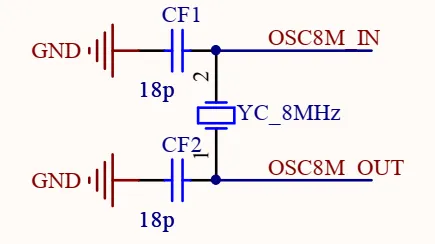

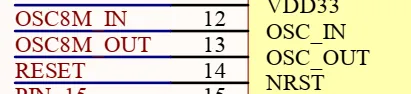

AGRV2K CPLD支持无源晶体做时钟输入,和AG32一样接入OSC_IN和OSC_OUT管脚。VE管脚文件设为PIN_HSE,如: clk PIN_HSE

ledout[0] PIN_31

ledout[1] PIN_32

....

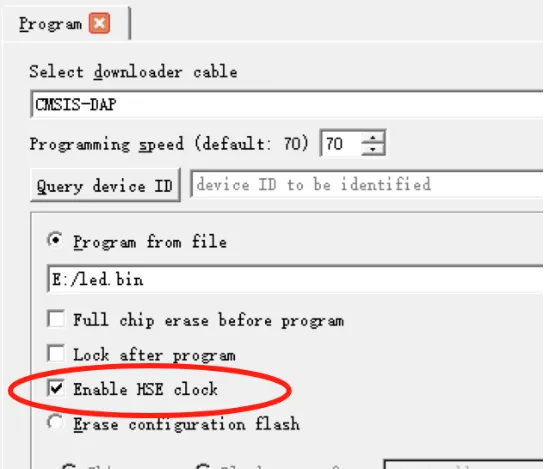

2.烧录下载选中Enable HSE clock

下载bin文件时,选中“Enable HSE clock”即可:

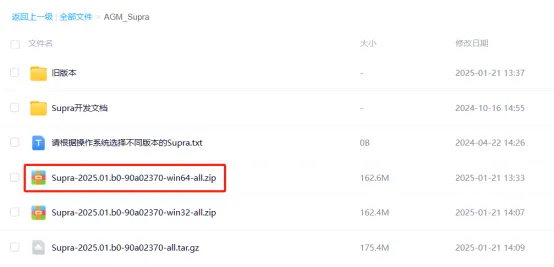

3.upra软件下载

最新Supra软件下载链接:

https://pan.baidu.com/s/1rJiAJHQQCp8WPGSPwCLm1Q?pwd=1234

如需了解更多资讯,欢迎联系海振远科技销售人员获取支持。