AGM AGRV2K逻辑设置详解

AG32 MCU内置的CPLD,可以与MCU配合使用,也可以作为独立的CPLD使用,本文介绍基于AG32 开发,如何对AGRV2K的逻辑设置进行配置。

1.器件配置

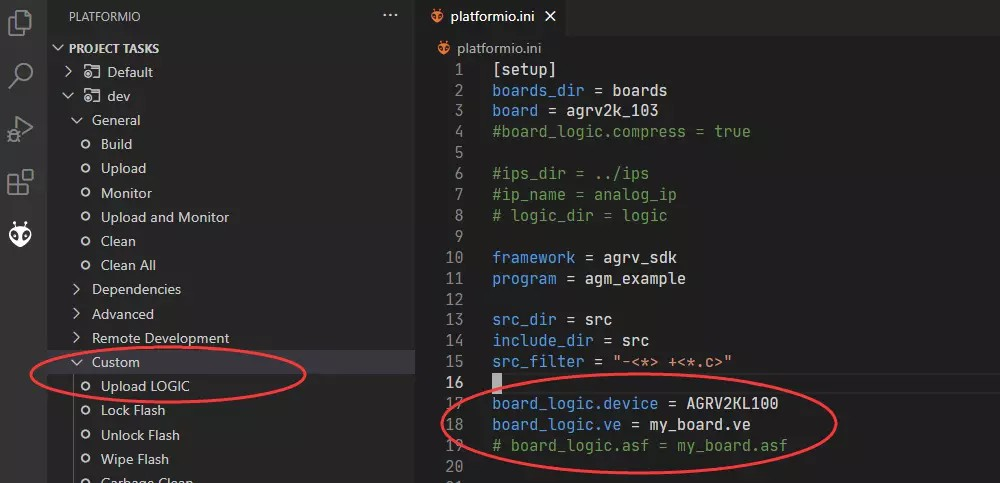

platformio.ini为PlatformIO的⼯程⽂件,所有⼯程设置均可以在这个⽂件中进⾏修改。

根据所使⽤器件修改board_logic.device,缺省为100PIN的AGRV2KL100。如果使⽤的是64或48PIN的器件,需要修改为AGRV2KL64或AGRV2KL48。

逻辑配置⽂件⼤⼩固定为100KB。⽀持压缩功能,压缩之后的⽂件⼤⼩与设计有关,但⼀般不会超过40KB。可以通过设置board_logic.compress=true来打开压缩,默认为false。逻辑配置⽂件默认占⽤内部flash的最后部分,可以通过board_upload.logic_address来改变。

2.引脚设置

通过逻辑改变引脚定义:在platformio.ini中加⼊:

将指定的ve⽂件放在platformio.ini同⼀⽬录下,然后点击PROJECTTASKS下的UploadLOGIC。VE⽂件格式为每个引脚⼀⾏,每⾏由Function_Pin和Device_Pin组成,可参考AgRV_pio\platforms\AgRV\boards\agrv2k_103\board.ve。Device_Pin由封装决定,⼀般为PIN_xx的形式。指定的VE⽂件名称可以是相对路径(基于当前项⽬⽬录,亦即platformio.ini⽂件所在⽬录)或绝对路径。

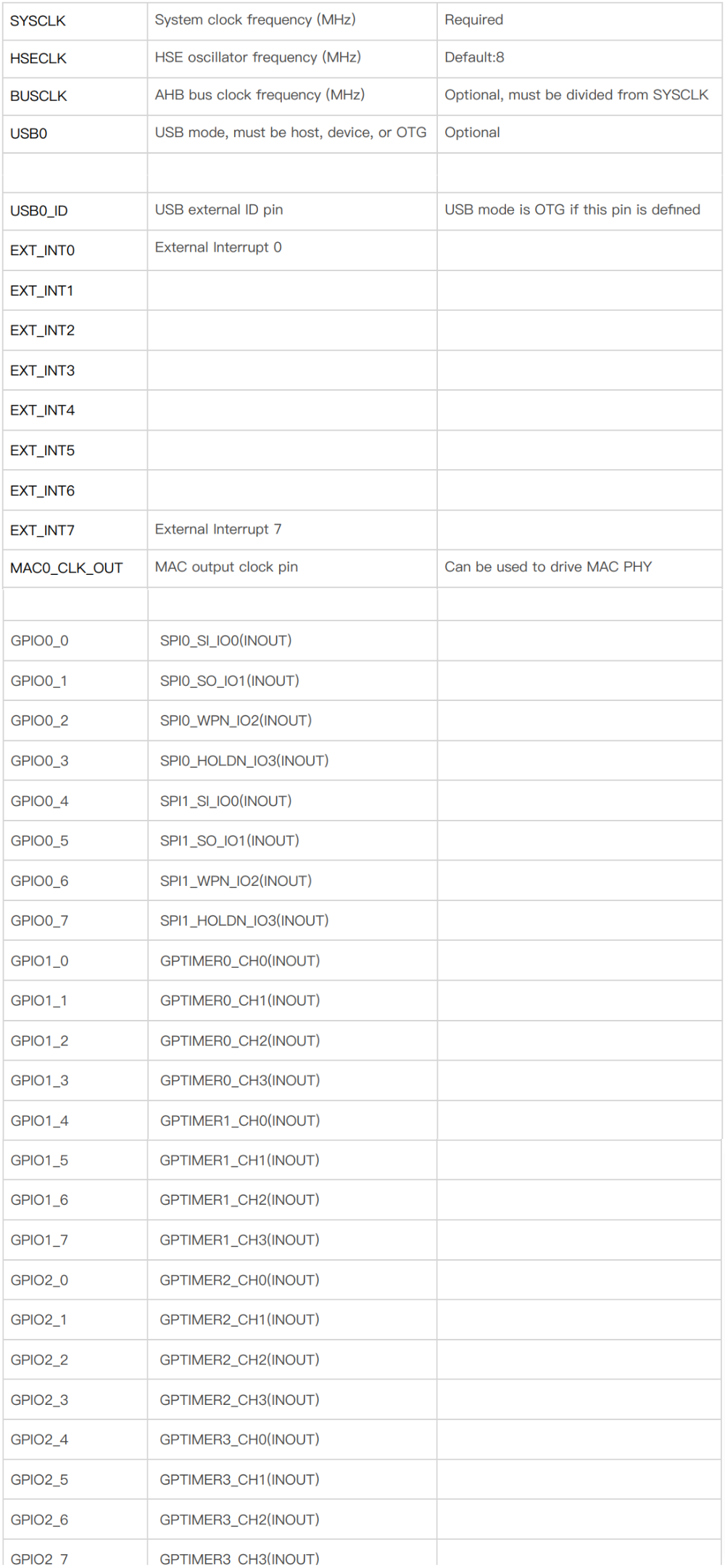

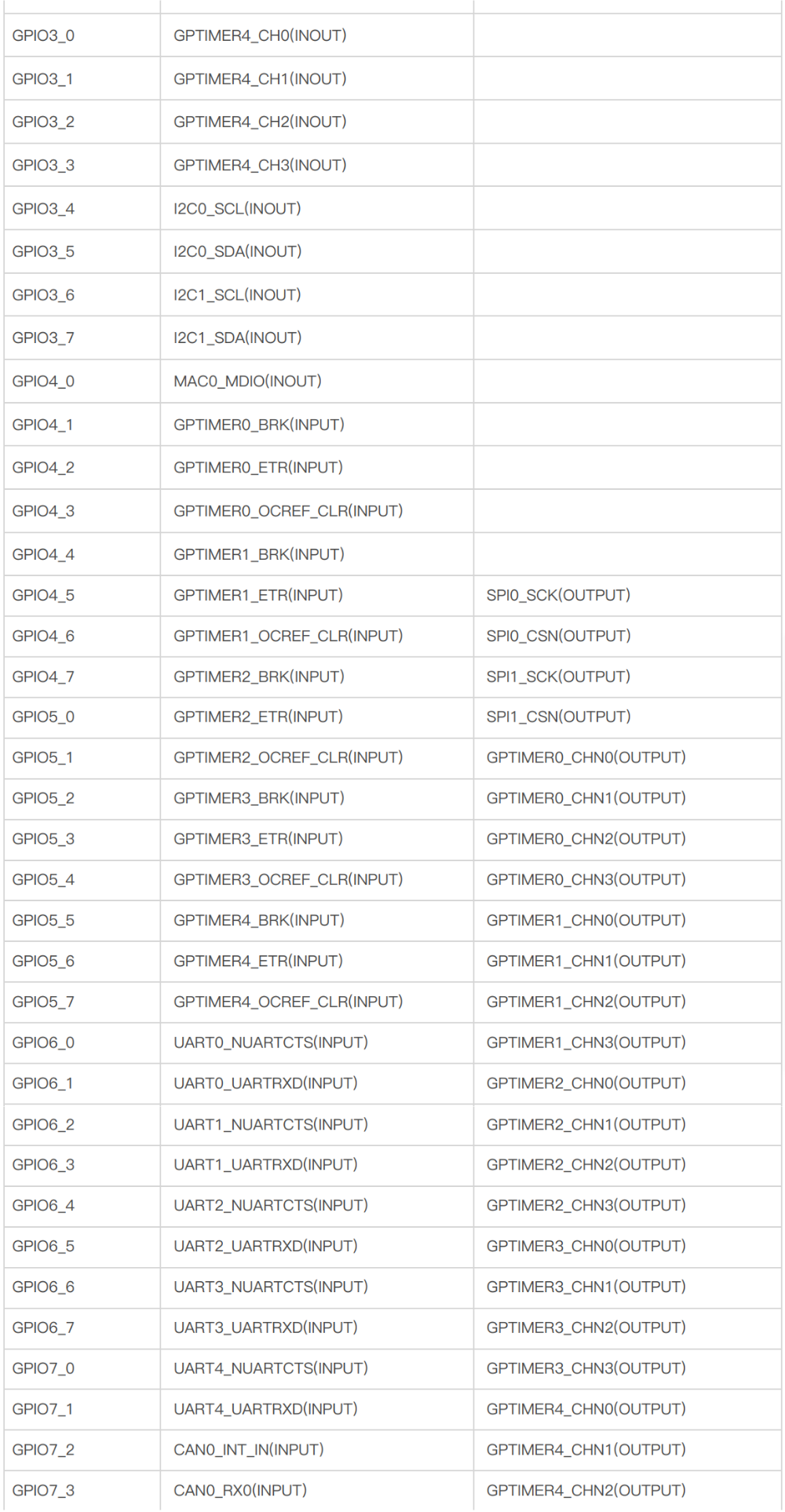

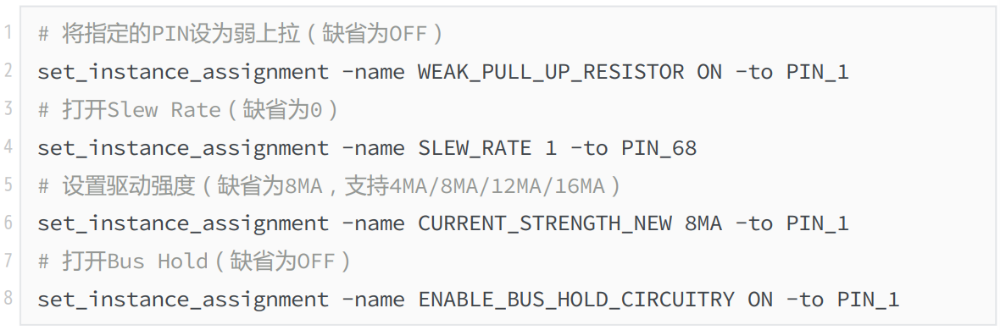

Function_Pin列表:

每⼀⾏的GPIO和外设引脚同⼀时间只能使⽤⼀个,可以在程序中使⽤GPIO_AF_ENABLE(MAC0_MDC)或GPIO_AF_DISABLE(MAC0_MDC)来打开或关闭外设。同⼀⾏的输⼊和输出外设引脚可以同时使⽤,例如UART1_UARTRXD可以和GPTIMER2_CHN2同时使⽤,但使⽤了⼆者任意⼀个均不可使⽤GPIO6_3。

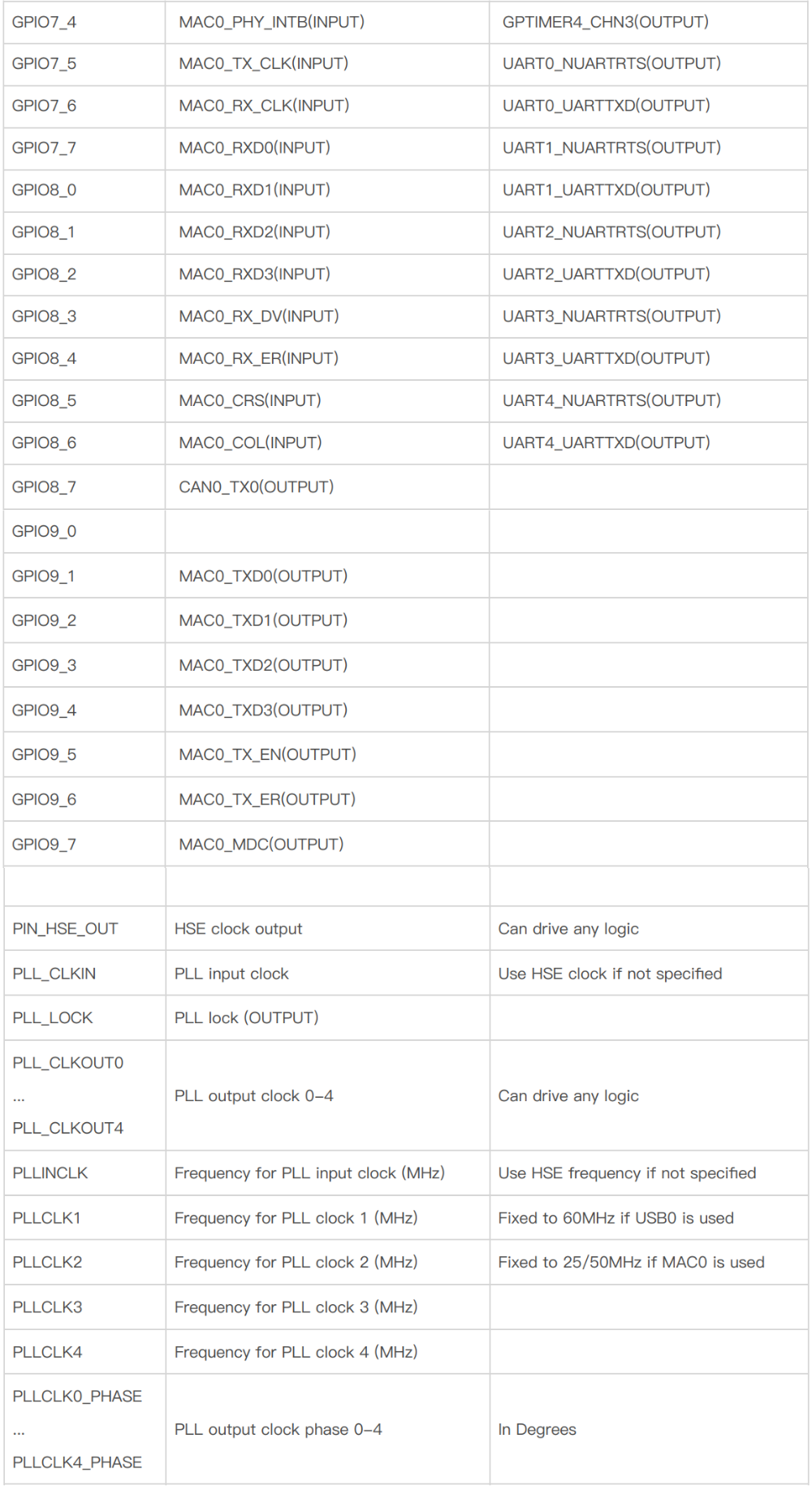

每个引脚的其他设置可以通过在platformio.ini中指定board_logic.asf来实现:

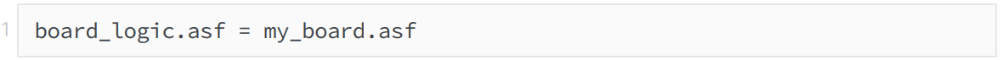

在指定的asf⽂件中加⼊具体设置:

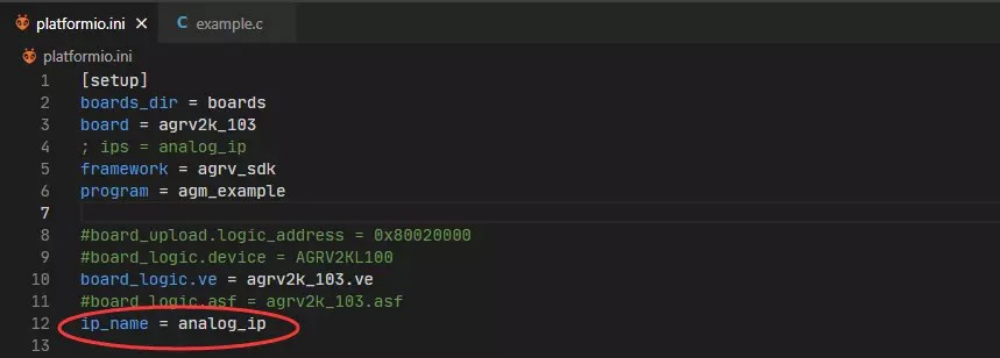

3.预定义IP

在platformio.ini中加⼊:ip_name,然后同上点击UploadLOGIC。预定义逻辑不能与⾃定义逻辑同时使⽤。

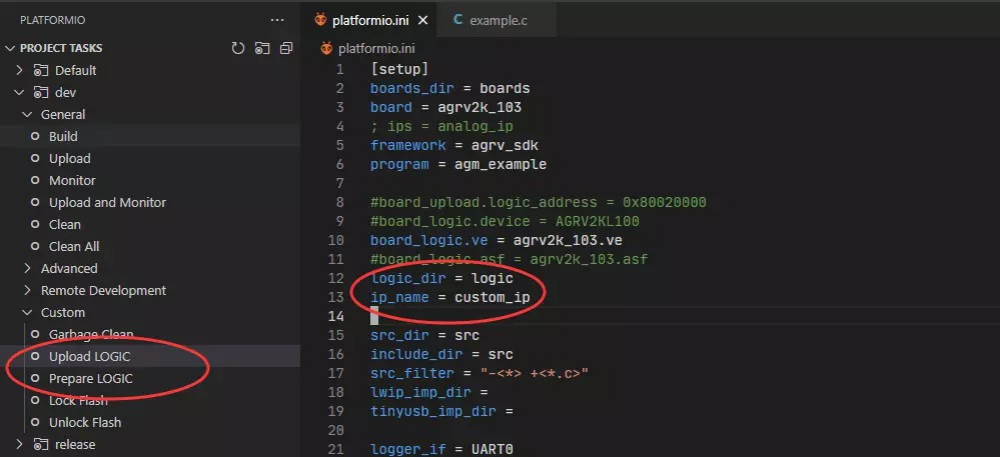

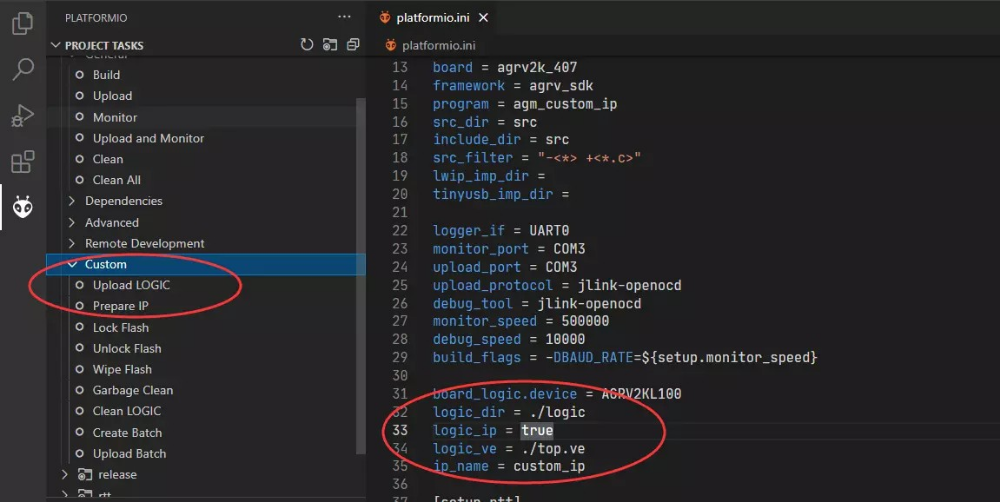

4.⾃定义IP

在platformio.ini中加⼊logic_dir和ip_name。logic_dir是存放⾃定义逻辑的⼦⽬录,如果该⽬录不存在将⾃动创建。ip_name为⾃定逻辑的模块名称,不能与预定义IP同时使⽤。然后点击PROJECTTASKS下的PrepareLOGIC,⼯具将在指定的⽬录下产⽣⼀个Supra⼯程,⼯程⽂件以上图为例是.\logic\agrv2k_103.proj。Supra软件可以通过AgRV_pio⽬录下的快捷⽅式Supra.exe启动,在软件中打开这个⼯程⽂件并选择Tools->Compile,详细使⽤请参⻅Supra的使⽤⼿册。在Supra⼯具成功编译完成之后,再点击UploadLOGIC更新逻辑配置。以上图为例,逻辑配置⽂件将产⽣于.\logic\agrv2k_103.bin。例程可参考AgRV_pio\platforms\AgRV\examples\analog。

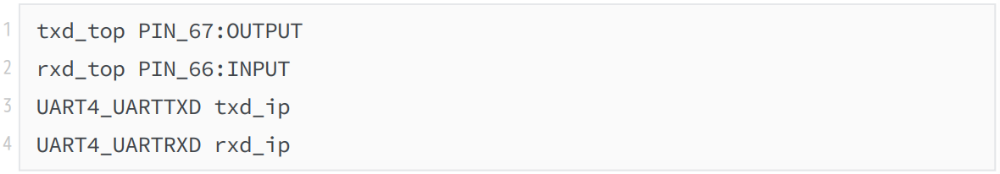

⾃定义逻辑的ve⽂件中除上述"Function_PinDevice_Pin"的引脚设置外,还可以加⼊另外两种引脚设置:

1.与⾃定义逻辑连接的顶层管脚,格式为:"NameDevice_Pin:DIR",DIR可以是INPUT,OUTPUT,或者INOUT。⼯具将把⼀个指定⽅向的管脚加⼊⾃定义逻辑,并连接到对应的芯⽚顶层管脚。

2.与⾃定义逻辑连接的某个MCU功能,格式为:"Function_PinName"。根据Function_Pin的⽅向,⼯具将⾃动在Name后⾯加⼊后缀_in(⽤于驱动Function_Pin输⼊),以及_out_data/_out_en(⽤于接收Function_Pin的输出数据和使能)作为⾃定义逻辑的管脚。

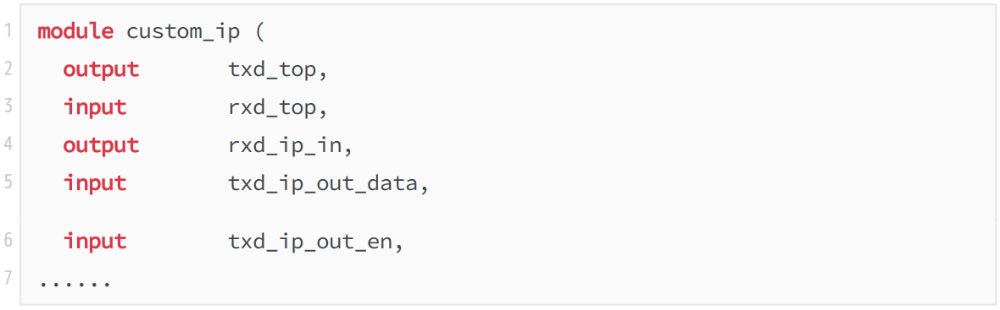

⾃动创建的Supra⼯程缺省将包含两个Verilog⽂件,分别对应芯⽚顶层和⾃定义逻辑模块。以上⾯为例名称分别是agrv2k_103.v和custom_ip.v。其中芯⽚顶层⽂件agrv2k_103.v每次运⾏PrepareLOGIC的时候都会根据ve⽂件⾃动⽣成覆盖,请勿⼿⼯修改。⾃定义逻辑模块⽂件custom_ip.v则不会被覆盖,如果已经存在,新⽣成的⽂件将被命名为custom_ip_tmpl.v。⽣成的⽂件中包含根据ve⽂件⽣成的所有⾃定义逻辑模块管脚。

例如⼀个下⾯的ve配置:

将⽣成如下的⾃动逻辑模块:

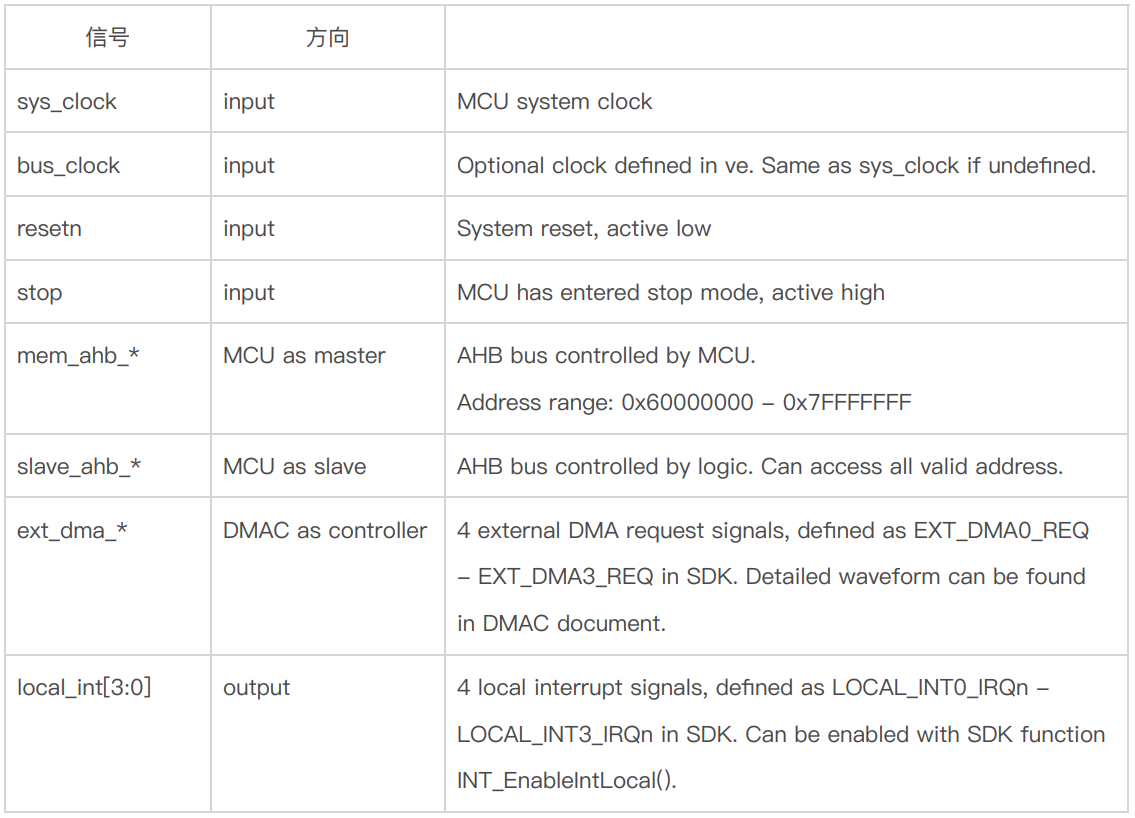

除根据ve⽂件⽣成的管脚外,⾃定义模块中还包含以下信号与MCU连接:

5.可移植IP

上述的⾃定义IP可以被转化成可移植IP,供其他AGRV2K⼯程使⽤。在platformio.ini中除logic_dir和ip_name外,再加⼊logic_ip:

然后点击PROJECTTASKS下的PrepareIP,⼯具将在指定的⽬录下产⽣类似⾃定义IP的Supra⼯程。这个⼯程的顶层模块即是⾃定义逻辑的顶层,不包括芯⽚顶层。⼀切设置,包括时序约束,都应当基于⾃定义逻辑的顶层。使⽤Supra编译好之后,可移植IP的⽬录位于指定的logic_dir\ip_name下。以上图为例,⼯程的顶层模块是custom_ip.v,可移植IP的⽬录是logic\custom_ip。例程可参考AgRV_pio\platforms\AgRV\examples\custom_ip。

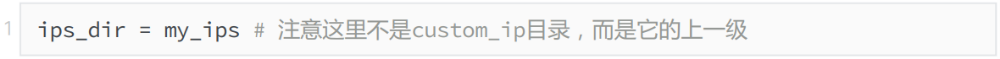

使⽤可移植IP的时,把上⾯⽣成的custom_ip⽬录放在任意⽬录下,例如my_ips。然后在platformio.ini中加⼊ips_dir来指定这个⽬录(如果在同⼀个⼯程中使⽤可以跳过这⼀步):

点击PROJECTTASKS下的UpdateLOGIC,即可⽣成以及下载基于可移植IP的逻辑配置。这⾥使⽤的ve⽂件与⽣成可移植IP时使⽤的ve⽂件相⽐,必须满⾜如下条件:

由"Function_PinDevice_Pin"定义的管脚可以随意改变,也可以增减,因为它们与IP没有连接关系

由"NameDevice_Pin:DIR"和"Function_PinName"定义的管脚,Name不得改变,Device_Pin以及Function_Pin则可以改变,也就是说同⼀个IP管脚可以在使⽤的时候映射到不同的顶层管脚或是MCU功能。

更多的资讯,欢迎邮件或者电话联系我们。