一、AGM AGRV2K的介绍

AGVR2K 是一款低成本的CPLD。这种上电即可运行、非易失性CPLD系列针对通用和低密度逻辑应用。逻辑密度为2K逻辑元件,采用LQFP-100(AGRV2K100), LQFP-64(AGRV2K64)和LQFP-48(AGRV2K48)封装。

产品特性:

低成本、低功耗CPLD

即开、非易失性标准兼容架构。

在驱动整个设备的全球时钟网络中最多4个全球时钟线。

提供可编程的快速传播延迟和时钟到输出时间。

每个器件提供锁相环,时钟倍增和相移。

支持3.3 v逻辑电平

可编程转换率,驱动强度,总线保持,可编程上拉电阻,开漏输出,施密特触发器和可编程输入延迟。

内置联合测试行动组(JTAG)边界扫描测试(BST)电路投诉符合IEEE标准1149.1-1990

ISP电路符合IEEE标准1532

3.3 v LVCMOS和LVTTL标准

二、针对AGM AGRV2K的开发设计流程

1.软件安装

解压缩或执行安装文件, 安装Supra 软件。执行文件为 bin 目录中的 Supra.exe。 运行Supra,选择菜单 File -> Import license ,选择 license 文件并导入 License。

2.新建项目

新建一工程目录。打开 Supra ,在目录中新建 project。

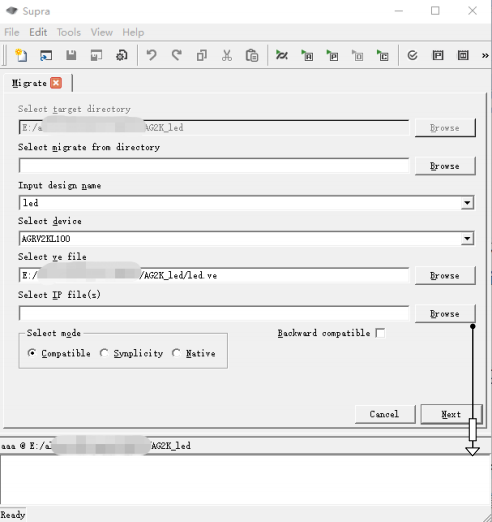

进入 Tools -> Migrate:

Target Directory 默认为新建的工程目录, Migrate from directory 不填, 输入设计名称(这里 例如 led), Device 选 AGRV2K 系列型号。选择 ve 文件 (管脚分配文件)。IP 文件不用。

选择对应开发 Mode :Native 选项(AGM 自有 EDA 综合工具),Synplicity 选项(第三方综 合工具,例如 Synplify ,Mentor 等),Compatible 选项(兼容 Altera Quartus II 的综合工具)。

下面主要介绍 Supra 基于 Quartus II 综合的设计流程,其它工具设计流程类似。Mode 选择 Compatible,点 next , 生成一个以 led 命名的 Quartus II 项目,以及空的设计文件(qpf ,v, sdc 等)。

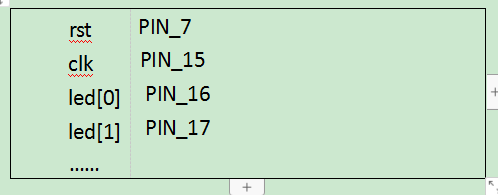

ve 文件为 IO 管脚位置设置,可通过任意文本编辑器自行编辑产生。管脚名称请参考前面的 管脚说明表格(PIN_1 ,PIN_2 格式),全局信号最好选 IO_GB 管脚。

ve 文件格式如下(管脚设计名称+空格+封装管脚名称):

3.项目设计

用 Quartus II 打开 led.qpf 项目文件, 工程已设置好,不要修改型号。加入你的设计文件v, 或添加其它所需设计源文件。

设计完成后,Quartus II 中选择菜单中 Tools -> Tcl Scripts...,窗口中选 af_quartus.tcl,点击 Run 进行编译,综合产生网表文件。

AGRV2K 器件支持 1 个 PLL。若需用到 PLL,可以在 quartus 工程中直接添加 IP (ALTPLL)。

4.项目编译

Supra 里继续执行 Next ,开始进行编译。 编译选项,默认即可。

编译成功后可以得到烧写文件, led.bin。

以后修改设计,Quartus 里只需执行正常的编译( Start Compilation), 可以不用再运行

af_quartus.tcl 文件。然后在 Supra 中打开 Tools -> Compile ,完成编译即可。

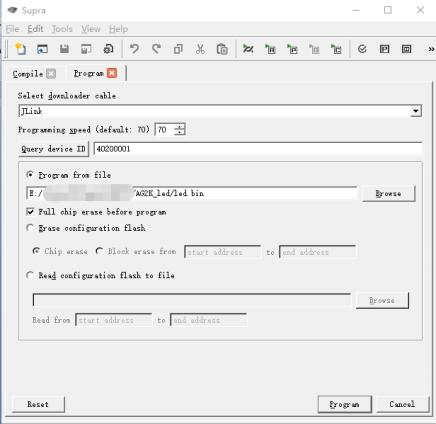

5. 芯片烧写

Supra 软件中选 Tools –> Program ,下载线选 JLINK。速度默认即可。

可以先点击 Query device ID,查看是否检测到器件, 正确 ID 为: 40200001

选择编程文件 led.bin,点击 program 开始烧写文件。如没有出现错误信息弹出, 显示“done with code 0”,即烧写成功,程序开始运行。