AGM AGRV2KQ32 ---硬件设计要点

AGM AGRV2KQ32 超小封装FPGA,电路设计简单。为了帮助用户快速画板设计,分享一下设计的注意事项。

一、AGRV2KQ32的引脚定义

| QFN-32 | Pin name | AG32VFxxxK | AGRV2KQ32 |

| 1 | PIN_1 | IO/RTC | IO_GB |

| 2 | PIN_2 | IO/OSC_IN | IO |

| 3 | PIN_3 | IO/OSC_OUT | IO |

| 4 | NRST | NRST | NRST |

| 5 | PIN_5 | IO_ADC_IN12 | IO |

| 6 | VDDA33 | VDDA33 | VDDA33 |

| 7 | PIN_7 | IO_WKUP_ADC_IN0_CMP_PA0 | IO |

| 8 | PIN_8 | IO_ADC_IN1_CMP_PA1 | IO |

| 9 | PIN_9 | IO_ADC_IN2_CMP_PA2 | IO |

| 10 | PIN_10 | IO_ADC_IN3_CMP_PA3 | IO |

| 11 | PIN_11 | IO_ADC_IN4_CMP_PA4_DAC0 | IO |

| 12 | PIN_12 | IO_ADC_IN5_CMP_PA5_DAC1 | IO |

| 13 | PIN_13 | IO_ADC_IN6 | IO |

| 14 | PIN_14 | IO_ADC_IN7 | IO |

| 15 | PIN_15 | IO_BOOT1 | IO |

| 16 | VDD33 | VDD33 | VDD33 |

| 17 | GND | GND | GND |

| 18 | PIN_18 | IO | IO |

| 19 | PIN_19 | IO | IO |

| 20 | PIN_20 | IO_UART0_TX | IO |

| 21 | PIN_21 | IO_UART0_RX | IO |

| 22 | PIN_22 | IO_USBDM | IO |

| 23 | PIN_23 | IO_USBDP | IO |

| 24 | PIN_24 | IO_JTMS | JTMS |

| 25 | PIN_25 | IO_JTCK | JTCK |

| 26 | PIN_26 | IO_JTDI | IO |

| 27 | PIN_27 | IO_JTDO | IO |

| 28 | PIN_28 | IO_JNTRST | IO |

| 29 | PIN_29 | IO | IO |

| 30 | BOOT0 | BOOT0 | GND |

| 31 | PIN_31 | IO | IO |

| 32 | VDD33 | VDD33 | VDD33 |

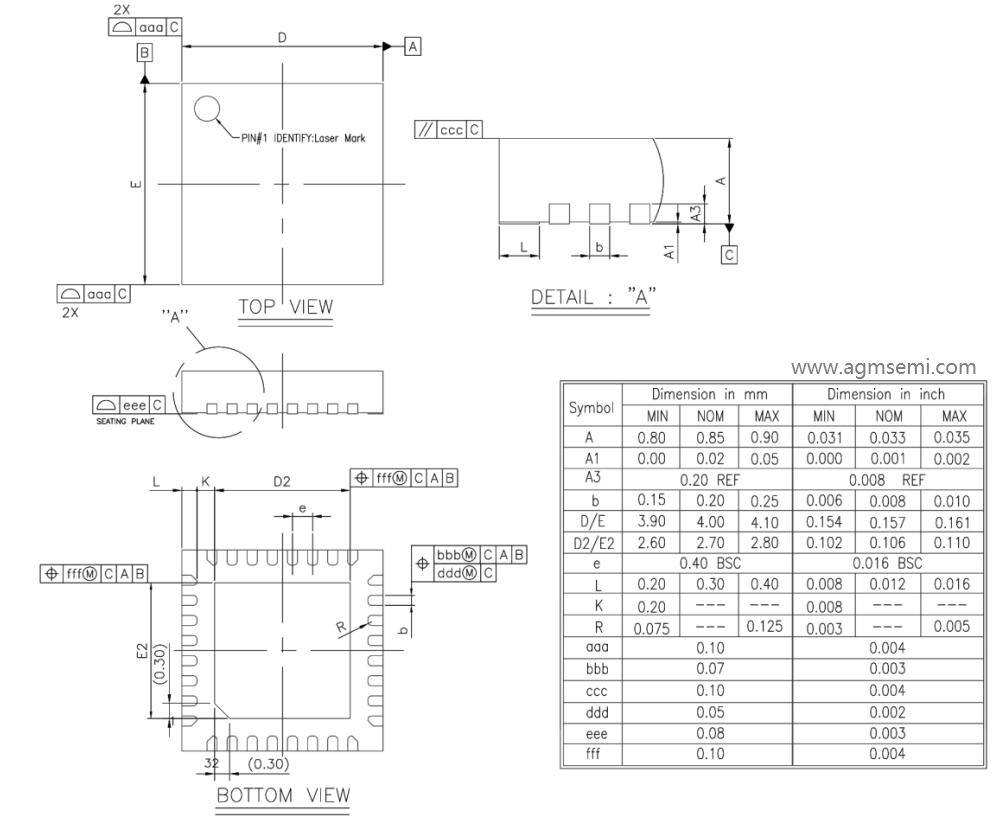

AGRV2KQ32芯片封装尺寸图:

二、设计要求

1、芯片的单电源3.3V供电,不需要1.2V;VDDA33 和VDD33都接到3.3V电源。

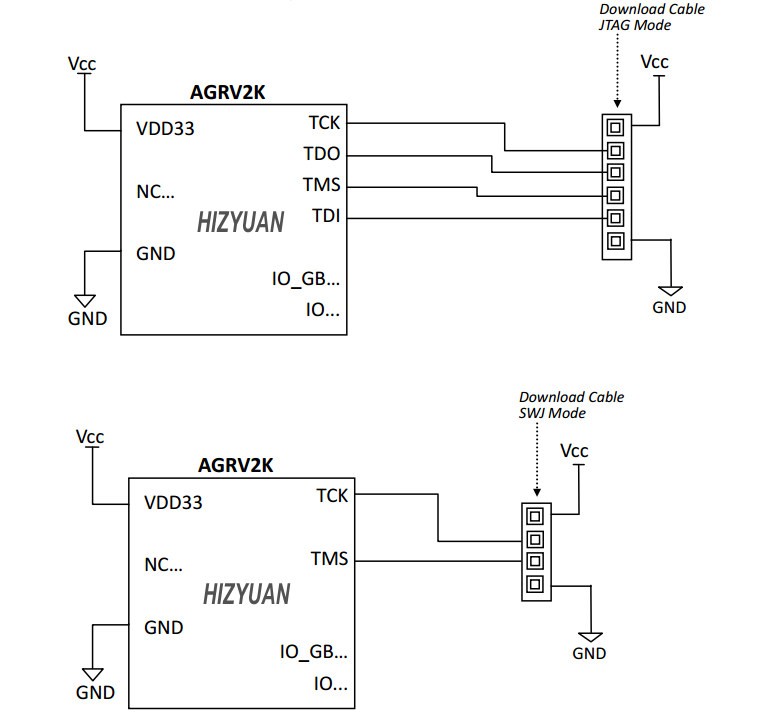

2、烧录只需要用JTCK, JTMS, GND, VCC 这4根线,即SWD模式进行调试烧录;

3、FPGA/CPLD推荐用有源晶振,晶振从IO_GB端口输入;

4、NRST可以做复位引脚,低电平复位。硬件设计可以悬空,也可以接0.1uF电容,实现上电慢复位。

5、芯片底部中间的焊盘接GND。

6、设计好原理图后,可以将FPGA部分的原理图设计发给AGM或者海振远的FAE检查确认。

AGRV2K被广泛应用于电机控制、测试测量,医疗和工控板上,产品的具有小封装,大容量,设计灵活等优点。