在一般的工程设计当中,只需要按照Supra快速入门文档,执行完全部操作,生成编程文件即可。若遇到时序不满足,比如功能跟设计的预期不一致,则需要考虑对时序进行优化。这里介绍一些Supra的高级功能,方便大家查询和使用。

1) 工程便捷编译

跳过 Migrate Setup,直接进入最后 Migrate Run 编译页面。选择菜单:“Tools->Compile”。

2) 工程编译高级功能

新增 Useful skew,Useful skew scope,Target timing 等,还有若干 Experimental 功能。请参考时序优化指南。

3) 进程结束提示信息

选择菜单:“File -> Settings”中:

Elapse time:超过此时间后在编译完成会有提示信息和铃声。Bell:提示音选择。

Popup message:弹出提示信息框。

4) Migrate 空的工程

Migrate 原工程目录(From directory)可以为空,这样在 Run 目录(Target directory) 产生个空的工程;AG1KLP,AG3K 等非兼容型号可以这样开始设计。

5) Compile flow

Migrate 最后编译前的设置界面里,或者选择菜单:“Tools -> Compile”。

l Default/Full:Full place and route;

l Route:只运行 route,使用以前的 placement 结果;

l Probe:probe 内部信号;

l Skip:只运行时序分析,不重新 place and route。

选用"Route"模式,重新 route 可能会碰运气得到更好的布线结果;

选用"Probe"模式可用于 PCB 板的在线调试,可以通过 IO 快速探测内部信号。

"From"填需要探测的管脚或 net 名称,"To"是引出探测信号的 IO 管脚,可使用闲置 IO。如果这个 IO 是设计中使用的,需要选中"Force",则强制引出到此 IO,否则就会编译出错。Probe 模式产生的编程文件和原设计的不同,会有"probe_"前缀。

6) Batch Mode

可以通过随机 seed 及其它编译选项,自动批量多次编译,以便从中选择最优结果;根据需要选择编译次数和并行运行数量。批量编译结果保存在 bc_summary.txt 文件,以及 bc_results 目录中。

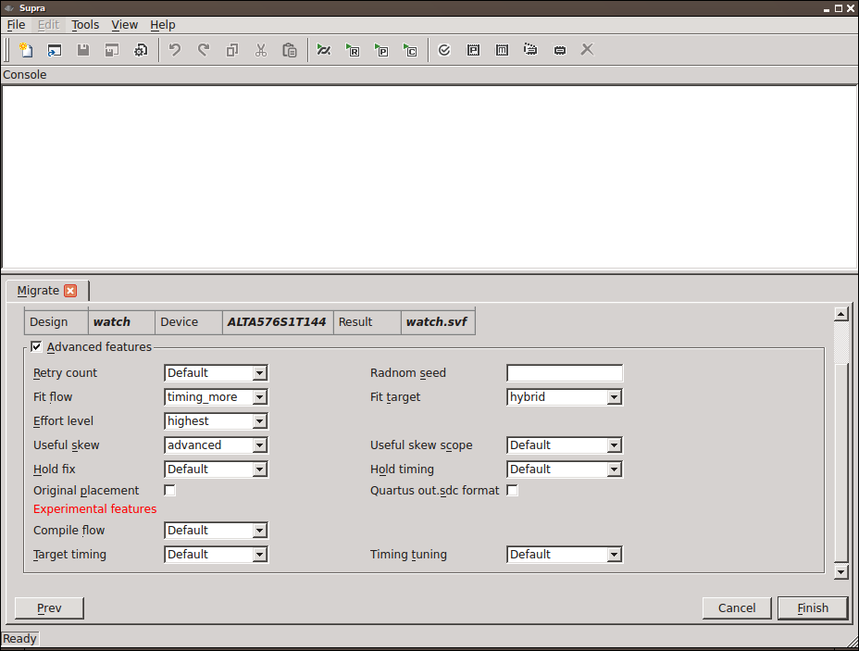

Migrate Run 界面里提供了一些Advanced Features 选项。这些选项可以针对不同的设计进行细分设定。第一次使用 Supra 的时候,会自动设定一组缺省设置。这些设置是综合以往的经验得到的最佳设定。如果通过这些缺省选项,不能得到满意的结果,则需要个别调整。www.agmsemi.com

一旦一个选项被重新设置后,新的设置则会被记录下来。

针对时序优化,其中有几个选项最为重要。下面基于其先后顺序进行详细解说。

1) Fit flow

调整routability 以及 timing 的 tradeoff 参数。推荐的默认设定是 timing_more,一般情况下会得到比较好的时序。其次是 timing 和 basic。

但如果设计比较拥挤,则可能有必要选取 routing 或者 routing_more。

2) Useful skew

通过调整时钟的 skew,从时序宽松的部分借来给时序紧张的部分,就像是劫富济贫。使用这个功能,对时序约束的要求比较高。如果欠缺一部分的约束,就可能把原本没有约束到但是其实时序紧张的部分反而拿来借给他处,造成额外的 violation。

鉴于上述的以及其他可能的副作用,要谨慎的使用该功能。应该先尝试不使用此功能。www.agmsemi.com 如果必须使用,需要从最基础的 basic 试起,其次是 advaned,最后再尝试 aggressive,boosted。随着设置 level 的增加,时序改善的可能性以及幅度都是相应增加,但是其副作用(如时序可能反而变坏)也可能会增加。

3) Useful skew scope

配合上述的 Useful skew 一起使用。指定 skew 影响的范围。all 是把Useful skew 运用到所有的单元,core 是把 IO 输入输出部分排除,logic 是指运用在 slice 逻辑单元(排除运算以及存储单元)。由于通常 IO 上的约束不是很完善,所以有可能需要不影响到相关的时序。运算以及存储单元的结构跟逻辑单元相差比较大,有必要区分出来。

缺省的情况下,2)的 Useful skew 设定是 basic 的话,相当于core,其他设定等同于 all。

如果编译结果报的时序没问题,但是实际上板子却出现时序问题,可以尝试逐渐选取其他设定。

4) Hold fix

保守的设计方式不太会产生大量的 hold 问题。一般 hold 问题主要出现在 IO 的input/output delay 上。这个设定的缺省是只改进 IO 上的 hold 问题。但是如果有比较复杂的时钟,譬如不同时钟之间有时序关联,或者时钟上有不同的逻辑单元,或者有 local 时钟, 则很有可能会产生内部的 hold 问题。这样就需要选择 basic 甚至 advanced 的了。主要这两个选项的对 fmax 的潜在影响会比较大。当发现有 hold 问题时,先排除 false path 的可能性, 不要轻易启动这两档设定。

5) Target timing

指定优化目标的时序范围。由于发现有一些设计没有充分定义 false path 以及 multi-cycle path 约束,导致离现实相差很大的时序。编译算法会用很多资源去尝试改进没有必要改进的时序,反而会影响到其他正常的时序。可以通过这个选项把最坏的时序截到目标时序附近, 进而排除掉一部分不现实的时序。这部分使用缺省的设定就可以了,偶尔必须时才需要调整设定。

6) Effort level

顾名思义,level 越高所花的编译时间越长,结果则可能会更好。一般建议选 highest。

如果时序要求不高,可以选择其他更低的 level。

7) Random seed

编译算法有随机性,通过改变 seed,有可能会产生更好的结果。但是一般对结果的影响没有上述的几个设置大。

seed 0 有特殊含义,每次编译的 seed 都是随机产生的。

小于 100 的 seed,随机性要小于大于 100 的 seed。如果对编译结果的稳定性要求比较高的话,请选择小于 100 的 seed。

相反,大于 100 的 seed,结果的稳定性较差,但有可能得到更好的结果。

8) Fit target

一般建议选用 hybrid。

如果编译结果不理想,可以尝试选择其他选项。

9)其他的设置

其他没有提到的设置,用缺省的设定就可以了。一般不需要改变设定。

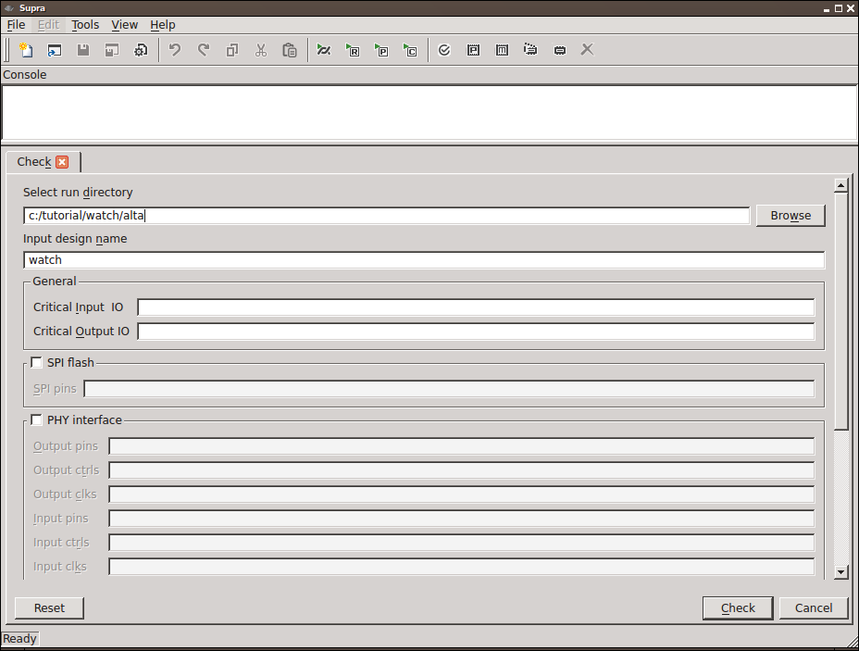

在当前工程目录下,产生一个<DESIGN>.chk 文件。在编译完成之后,就会自动进行设计规则检验。结果会放在 alta_db/check.rpt 文件里。

另外,也可以使用GUI(Tools->Setup rule check)进行设置。如下图所示:

<DESIGN>.chk 文件的内容如下:

set SPI_SPI “spi_sdi spi_sdo spi_sck spi_cs" set PHY_OUT “tx_data*”

set PHY_OCTRL "tx_ctl*" set PHY_OCLK "tx_clk*" set PHY_IN “rx_data*” set PHY_ICTRL "rx_ctl*" set PHY_ICLK "rx_clk*" set SDRAM_CHECK_METHOD 1

set SDRAM_DATA "sdram_data[*]"

set SDRAM_ADDR "sdram_add[*] sdram_ba[*]" set SDRAM_CTRL "sdram_ras sdram_cas sdram_we" set SDRAM_CLK "sdram_clk"

set SDRAM_CLOCK "sdr_clk_ext"

设计规则检验主要是针对AG10K 芯片,包括以下几个模块。具体要根据设计需求,指定相关的参数。设计中无关的模块,可以省略掉。

l Critical Input IO/Critical Output IO

如果这些 Critical IO 没有使用 fast_input_register,fast_output_register,会有警告信息;

l SPI Flash

SPI_SPI (SPI pins) 指定所有(4 个)SPI 的端口

l PHY Interface

PHY_OUT (Output pins)指定 PHY TX 输出数据端口PHY_OCTRL(Output ctrls)指定 PHY TX 输出控制端口PHY_OCLK (Output clks)指定 PHY TX 输出时钟端口

PHY_IN (Input pins ) 指定 PHY RX 输入数据端口PHY_ICTRL(Input ctrls) 指定 PHY RX 输入控制端口PHY_ICLK (Input clks ) 指定 PHY RX 输入时钟端口

l SDRAM Interface

SDRAM_DATA (Data pins)指定 SDRAM 输入输出数据端口SDRAM_ADDR (Address pins)指定 SDRAM 输出地址端口SDRAM_CTRL (Control pins)指定 SDRAM 输出控制端口SDRAM_CLK (Clock pins)指定 SDRAM 输出时钟端口

SDRAM_CLOCK (Output clock)指定时序约束里定义的 SDRAM 输出时钟

SDRAM_CHECK_METHOD (Method : recommend 1, recommend 2)

为了满足 SDRAM 输出端的时序,有两套不同的方法。

第一种办法,set SDRAM_CHECK_METHOD 1(Method : recommend 1)。跟输入端不同,输出端口不采用FAST_OUTOUT_REGISTER,而是通过清零 SDRAM 时钟 PLL 上的相位来满足时序要求。

第二种办法,set SDRAM_CHECK_METHOD 2(Method : recommend 2)。跟输入端相同,输出端口采用 FAST_OUTOUT_REGISTER,然后通过调整 SDRAM 时钟 PLL 上的相位来满足时序要求。

l Clock skew

FPGA 的电路设计上的 clock skew 是很小的,基本上可以忽略不计。但是由于设计方式的原因,譬如时钟电路上有逻辑,或者没有用全局时钟,或者不同时钟之间有关联,都会产生不可忽略的skew。进而对电路时序产生不良影响。

通过 Clock skew 检测,可以对较大的 skew 进行警告。对于这些警告,可以通过改进设计,完善时序约束(指定 false path 等)来消除。

l Clock cycle

有一些设计,有意无意的采用时钟上升下降沿的混搭。其结果,就是在某些路径上,实际用的是 half cycle。譬如 full cycle 是 8ns 的时钟,如果是 half cycle 的话,就会变成 4ns。4ns 对于一些稍复杂的路径,时序上会比较紧张。所以,建议在设计中应尽量避免 period 比较小的 half cycle。

通过 Clock cycle 检测,可以对period 较小的 half cycle 进行警告。对于这些警告,可以通过改进设计,完善时序约束(指定 false path 等)来消除。