AG32 MCU中CPLD使用基础(一)

前言:

AGM是AG32 MCU, 可编程SoC和异构MCU的解决方案提供商, 海振远科技可提供全系列的开发板及SDK资料,方便用户从0开始,快速上手开发。

AGM AG32 MCU和FPGA 目前广泛应用于工业,消费,测试测量和医疗等场景。

AG32内置的FPGA( AGRV2K) 可升级替代EP570, EPM1270, LATTICE XO2-256,XO2-640, XO2-1200 等。

AG32 的管脚可以灵活定义,引脚与STM32。并且内置2KLE FPGA, 非常适合MCU + FPGA/CPLD的应用场景。

目录

时钟配置与使用

1. 外部晶振与内部振荡器;

2. PLL倍频与分频;

3. cpld可用的时钟;

4. 几个时钟的设置限制;

5. cpld的最高频率;

时钟配置与使用

时钟配置与使用

1、 外部晶振 与 内部振荡器 的使用:

mcu和cpld联合编程时,整颗芯片需要一颗外部晶振。(芯片有内部振荡器,但误差较大,校准后有5%以内误差,参考后续介绍)该晶振是mcu和cpld公用的(没必要为cpld再单独提供一颗晶振)。

晶振可以是有源得,也可以是无源得。

【注:这里得外部晶振配置,跟单纯使用MCU是一样的】

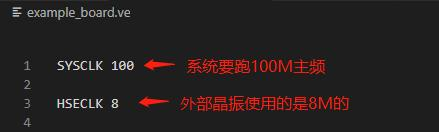

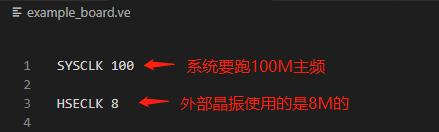

如果是无源晶振。频率限制再4M~16M.要接到芯片得OSC_IN/OUT引脚。VE中直接定义主频多少M即可。如:

(这是目前开发板上使用的配置)

如果是有源晶振,频率无限制。根据接入点分为两种情况:

1)如果接入倒OSC_IN引脚:

ve里定义同上(修改HSECLK项的值为有源晶振频率)。

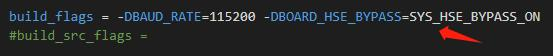

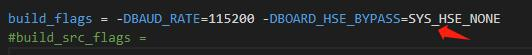

同时,需要在platformio.ini里增加配置:

BOARD_HSE_BYPASS=SYS_HSE_BYPASS_ON,

2)如果接入到别的IO引脚(如PIN_2):

VE配置中,除了配置HSECLK项外,还需要配置PLL_CLKIN项,如图:

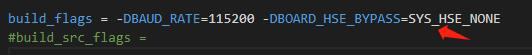

同时,需要在platformio.ini里增加配置:

BOARD_HSE_BYPASS=SYS_HSE_NONE

如果使用内部振荡器:

校准后精度大约在5%以内,节省成本且对时钟要求不高的话可以使用。

使用方式:

在VE里增加:"PLL_CLKIN PIN_OSC",如下图:

(注:不用配置HSECLK项)

同时在platformio.ini里增加配置:

BOARD_HSE_BYPASS=SYS_HSE_NONE

注:自动校准目前有以下使用限制:

a)逻辑部分要压缩,platformio.ini中配置:

board_logic.compress = true

b)校准动作是在烧录时进行的。

烧录时,需要使用swd方式且通过我们的软件烧录,uart不支持。

(即:出厂烧录不支持uart方式)

目前测试过jlink和dap校准结果都还不错,但是也出现过一个客户使用其他烧录器校准结果差很多。

(对一个全新的或是wipe过后的芯片烧录会看到校准信息)

2、PLL倍频及分频:

整颗芯片只有一个PLL倍频模块(mcu和cpld共用)。

倍频分频操作是封装在系统内部的(用户无须也不能控制这个时钟树)。

实现原理:

A.系统会根据所有用到的频率项(mcu和cpld要用到的全部频率),计算出他们的最小公倍数。该数值就是要倍频到的目标值;

B.以外部时钟作为输入,PLL倍频到这个目标值,然后再以这个目标值为基准,分频给mcu各外设和cpld来使用。

C.倍频和分频,无须开发者关注。

开发者只要设置好自己需要的各个时钟频率即可。

开发者可设置的频率分为mcu部分和cpld部分。

mcu部分,只需要关注系统主频。

主频是在VE里通过SYSCLK项配置,该主频是mcu的工作频率。

外设频率则基于这个主频再分频(参考各个外设的驱动部分)。

cpld部分,cpld最多可以输入5路不同频率的时钟。

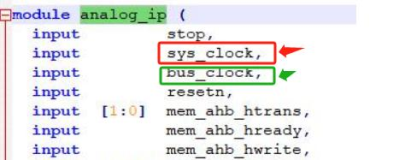

默认情况下,cpld工程接口中输入到cpld的sys_clock,就是跟mcu同频的SYSCLK系统时钟(由VE决定多少M)。

Bus_clock则是在SYSCLK基础上进行分频的另一路时钟(其实就是后续的PLLCLK3)。

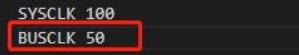

Bus_clock在VE中频率定义(必须是SYSCLK的整数倍分频):

如果ve里没有定义BUSCLK,则bus_clock和sys_clock同频。

bus_clock是为了防止cpld部分速度跟不上sysclk而设定的。

cpld中除了这两路(其实就是0路和第3路),还有3路可以使用。

3、 cpld可用的时钟(除去SYSCLK的另外4路):

cpld的时钟除了以上输入的sys_clock,还有4路可以独立使用。

参考《AGRV2K_逻辑设置.pdf》,如下图:

这里的PLLCLK1、PLLCLK2、PLLCLK3、PLLCLK4就是可使用的独立时钟。

注意:当mcu中使用USB时,PLLCLK1自动给了USB,不能再使用;当 mcu中使用了MAC时,PLLCLK2自动给了MAC,不能再使用。另外,上述的BUSCLK对应的是这里的PLLCLK3。如果用了BUSCLK的名字,这里的PLLCLK3就不能再用。

这里整理下5路时钟:

PLLCLK0:就是SYSCLK(名字使用SYSCLK)

PLLCLK1:开USB时,这路时钟给USB用(60M),不开USB时给用户用;

PLLCLK2:开MAC时,这路时钟给MAC用(25/50M),不开MAC时给用户用;

PLLCLK3:用BUSCLK时(只能是sysclk整数分频)不能用 PLLCLK3,否则可用;

PLLCLK4:独立给用户使用;

以PLLCLK3和PLLCLK4为例,说明怎么使用该时钟。

在VE里配置如下:

PLLCLK3 40 # 40MHz

PLLCLK4 60 # 60MHz

PLL_CLKOUT3 pll_clk3

PLL_CLKOUT4 pll_clk4

则可定义pllclk3为40M输入,pllclk4为60M输入。

在生成的cpld入口处,分别对应信号pll_clk3和pll_clk4,如图:

输入的时钟,可以跟sys_clock一样使用。

4、 几个时钟的设置限制及计算方式:

上边提到的倍频后PLL目标值,其数值关系需要满足:

A. PLL=HSE*X/Y,X,Y皆为整数

B. PLL小于1200MHZ。

C. 所有的设置频率必须能被这个最终PLL整除。

举例:mcu主频100M,系统用了MAC(50M),系统用了USB(60M),cpld自定义了

PLLCLK3为80M,cpld自定义了PLLCLK4为60M。则,PLL目标值就是100\50\60\80\60的最小公倍数,为1200M。

如果使用到一些特殊频率,则可以调整其他频率往这个特殊频率的倍数上来凑。

(如果配置后不满足这里的条件,编译时会报错)

5、 cpld可运行的最高频率:

mcu的运行最高频率是248M。而cpld中没有标准的最高频率。

最大能跑多少M,取决于cpld里的设计。

如果是逻辑电路,则不存在时钟的概念。

如果是时序电路,则看设计中门电路的复杂程度。如果跑100M的时钟,每个上升沿之间就是10纳秒,在设计时,要保证10纳秒内对应的动作能全部执行完。

如果是简单电路,一般是可以跑到200M以上。

补充信息:

AG32概述:

AG32系列32位微控制器旨在为MCU用户提供新的自由度和丰富的兼容外设以及兼容的引脚和功能。AG32VF407产品系列提供卓越的品质、稳定性和非凡的价值。

器件特征:

■ 最大 CPU 速度为 248 MHZ

■ 从 Flash 执行零等待

■ SRAM 128KB.FLASH 1MB

■ 支持浮点

■ 1个CAN2.0.5个UART2个I2C

■ 2 个基本定时器,5 个高级定时器

■ 支持 SDIO 、以太网 MAC

■ 支持 USB FS+OTG

■ 看门狗

■ 3个 12 位、最高 3M SPS ADC(17 通道)、2个 DAC

■ 2x 比较器

■ RTC, SPI

■ 内置2KLE FPGA逻辑单元

联系海振远科技

电话: 0755-2780 9180 ; 15323895320 ;

邮箱: tech@hizyuan.com

Lucy@hizyuan.com